昨兒個(gè)讀了《Write Greate Code》Volume1: Understanding the Machine

想通了很久困惑的問(wèn)題���,受益匪淺��,貼圖以共享

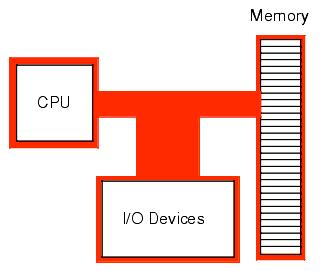

1. 約翰.馮.諾伊曼體系結(jié)構(gòu)(Von Neumann Architecture,VNA)

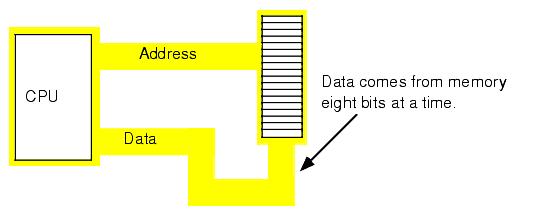

2.內(nèi)存物理組織

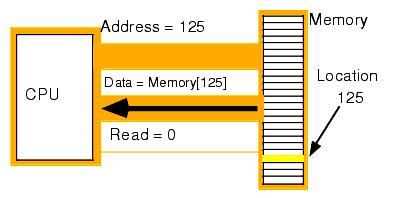

Read

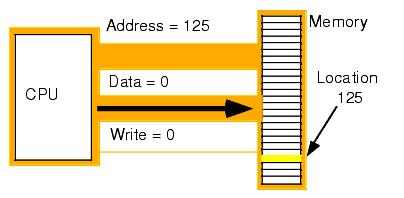

Write

3.地址總線

8bit

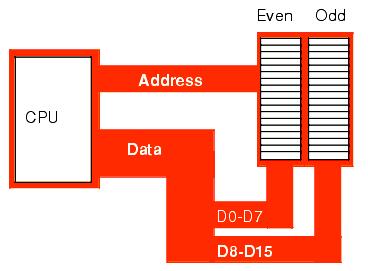

16bit

Say more here, there are a concept named bank which confused me when I read <Intel Architecture Software Developer's Manual>. The?physical memory is organized into two banks, even and odd, in 16 bits data addr bus.

So, 16 bits x86 CPUs always put even addr on the addr bus, and if they access odd addr, the CPUs must op memory twice.?

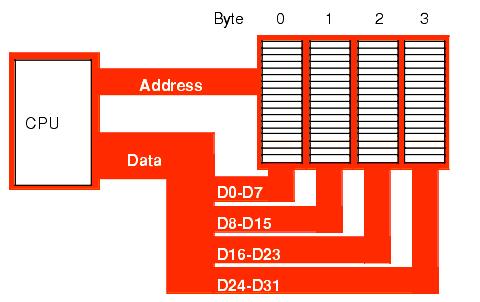

32bits

As with 16 bits, 32bits x86 CPUs always put 4X addr on?their addr bus.?

4. Byte Genders

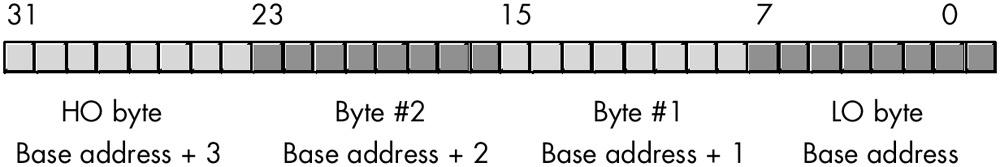

Little Endian

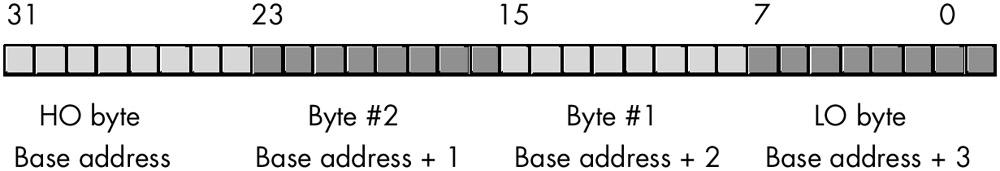

Big Endian

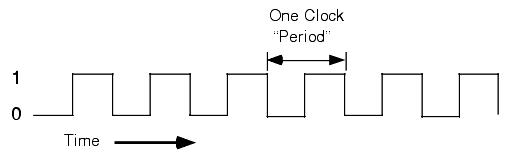

5.?System Clock

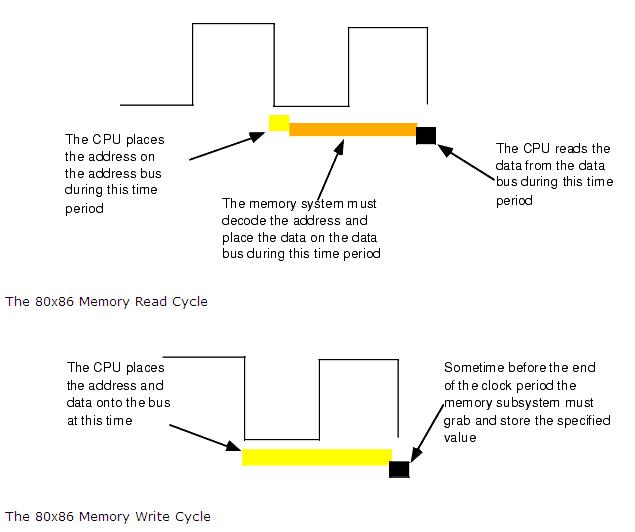

6.?內(nèi)存訪問(wèn)

內(nèi)存訪問(wèn)時(shí)間:從CPU講地址放到地址總線上開始到CPU從數(shù)據(jù)總線上取得數(shù)據(jù)之間的時(shí)間���。

x86 CPU,具有單周期內(nèi)存訪問(wèn)時(shí)間

等待狀態(tài)——(CPU)別跑那么快,等等我(IO)

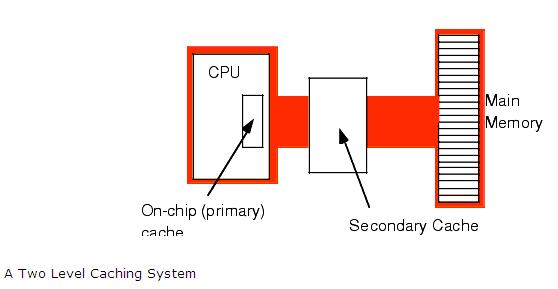

Cache-引用的時(shí)空局部特性(temporal and spatial locality of reference)

7.?內(nèi)存尋址模式

直接(direct), 間接(indirect),?變址(indexed),?比例變址(scaled indexed)

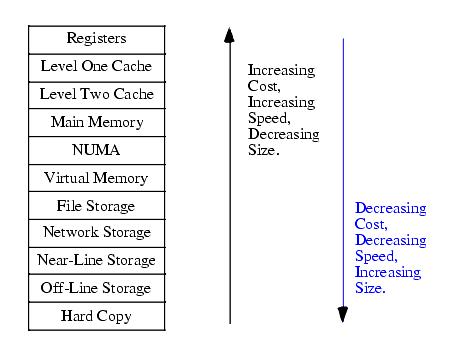

8.?內(nèi)存層次結(jié)構(gòu)(hierarchy)

說(shuō)一下NUMA,非一致內(nèi)存訪問(wèn)(Non-Uniform Memory Access)��,NUMA本來(lái)是說(shuō)不同類型的內(nèi)存有著不同的訪問(wèn)時(shí)間���,此處用來(lái)描述一些電氣上與主存類似��,但由于其速度比主存低很多的內(nèi)存���。一如��,顯存,閃存���。

So...,?that's all for today :p

?

posted on 2006-11-29 11:19

Charles 閱讀(732)

評(píng)論(0) 編輯 收藏 引用 所屬分類:

讀書作筆記